逻辑电平 admin 17/07/12

说明

我们生活在一个模拟信号的世界。然而,在数字电子技术里,只有两个状态–“开”或“关”。 利用这两种状态,设备编码,传输,控制大量的数据。逻辑状态,在广泛的意义上,描述了一个信号可以有的 任何具体、离散的状态。在数字电子技术,一般只有两个逻辑状态二进制的“0”和二进制“1”。

本教程包含

- 什么是逻辑电平?

- 在数字电路逻辑电平标准。

- 不同的技术之间的接口。

- 电平转换

什么是逻辑电平?

简单地说,逻辑电平是一个信号可以取的特定电压值或状态。 也就是我们经常提到的“开/关”、“通/断”、“高/低”、“1/0”。在过去的30多年中,电子电路已经发展出 多种电平的技术标准。

逻辑0和逻辑1

数字电子依靠二进制逻辑存储、处理、和传输数据或信息。 二进制逻辑是指一个状态(如:“高/低”)。这通常代表了二进制数“1/0”。

一个信号的强度可由其电压值来描述。通常,厂商的芯片的 《规格表》会给出的逻辑0(低)或是逻辑1(高)的定义。最常见的标准的TTL(晶体管-晶体管逻辑)。

低电平有效和高电平有效

使用集成电路和单片机的时候,你可能会遇到高电平引脚和低电平有效和引脚, 高电平有效有效。简单地说,如果要激活一个引脚功能。必须把引脚电平拉低(接GND)那就是 “低电平有效”,反之,如果要激活一个引脚功能,必须把引脚电平拉高(通常为3.3V/5V的)。就是 “高电平有效”

例如,一个移位寄存器有一个芯片使能引脚——CE。 如果你看到 《数据表》中CE上面有一条划线,CE, 那么,该引脚为低电平有效。需要把这个CE引脚拉至GND ,才能激活芯片。反只,如果CE引上没有划线,那就是高电平有效,需要拉高(接3.3V、5V)管脚才能激活芯片。

许多集成电路同时具有低电平有效和高电平有效的引脚。 我们需要仔细检查管脚名称。划线代表“相反”。所以,如果一个高电平有效的引脚,它的“相反”就 是低电平有效。就这么简单!

TTL逻辑电平

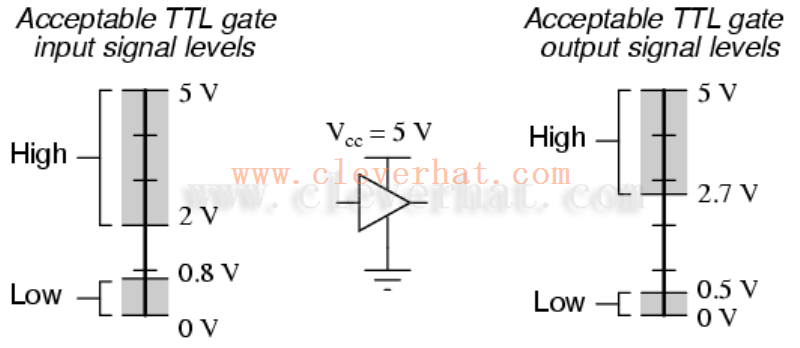

很多电路采用5V TTL逻辑电平。TTL是晶体管-晶体管逻辑的缩写。 依赖于电路由双极型晶体管电路实现。晶体管基本上都是工作在开关状态。任何逻辑系列, 都有多个阈值电平值:

vOH–设备向外输出一个高信号时,输出信号至少要达到的电平值。

vIH–被设备认为是高信号时,输入到设备的最小电压值。

vOL–设备向外输出一个低信号时,输出信号至多可达到的电平值。

vIL–被设备认为是低信号时,输入到设备的最大电压值。

你会注意到最小输出高电压(VOH)2.7 V。 这意味着该设备的驱动输出的高电压会总在2.7 V以上,最小输入高电压(VIH)是2伏, 这意味着任何高于2V的输入信号,将被识别成逻辑1(高)。

你也会注意到这里一个设备输出和另一个的输入之间的有0.7 V差值。 这个值被称为“噪声容限”。

同样,最大输出低电压(VOL)为0.4 V,这意味着一个设备试图发送 一个逻辑0时,其输出始终低于0.4 V。最大输入低电压(VIL)为0.8 V,这意味着只要输入信号 低于0.8 V就将被作为逻辑0(低)读入装置。

如果信号电平是在0.8 V和2 V之间的又会怎样呢? 这个范围内的电压是不确定的, 处于无效状态,通常被称为“浮动”状态。如果你的设备上输出引脚是“漂浮”在这个范围内, 没有明确的信号会导致什么呢?它可能被随机地识别成高和低。

下图给出了一个通用的TTL器件的输入/输出容差。

你将遇到的另一个常见的电压标准,是3.3 V设备标准。

3.3 V的CMOS逻辑电平

随着技术的进步,已经发展出了低功耗和运行电压较低的设备 (Vcc= 3.3 V,5 V)。制造技术也有所不同的3.3 V设备,具有更小的尺寸 和更低的整体系统成本。

为了确保兼容性,你会发现大部分的电平值同5伏的设备几乎都是一样的。 一个3.3伏的设备接口和一个5V的设备,不需要任何附加电路,可以直接对接。例如,从一个3.3伏设备输出的 逻辑1(高)至少2.4V,这在5V的系统里仍然会被解释为逻辑1(高),因为2.4V仍超过了VIH=2V.

然而,在反方向上,从5V设备的输出接至3.3 V设备的输入,为保证兼容。 你需要考虑的是3.3V设备的最大输入电压。对于3.3伏设备,3.6伏以上的任何输入电压会造成芯片永久性损坏。 你可以使用一个简单的分压电路将5V信号降低至3.3 V